# Introduction

The aXiom AX198A-2D is a Capacitive Multi-touch controller with the very highest performance, for use in demanding applications across markets such as Automotive, Industrial, White Goods and Medical.

The high performance acquisition engine enables the touchscreen controller to sense regular contacts and gloves. It also allows designers to use thick plastic front lenses and even to sense through a small air gap. Industry leading water rejection and wet finger tracking is also included.

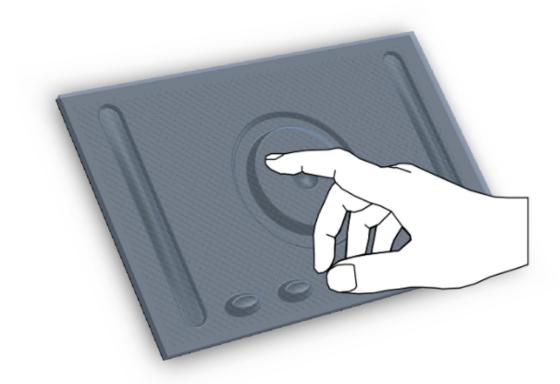

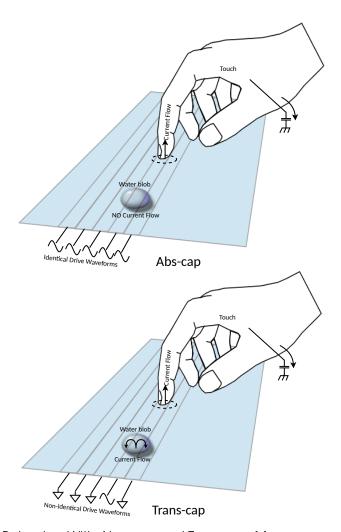

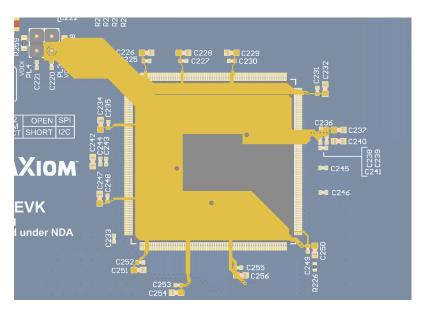

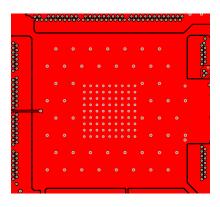

Figure 1-1: aXiom 2D Touch Sensing

A Windows<sup>TM</sup> based software package, TouchHub, is provided with the AX198A-2D to ease design and tuning tasks. This allows the designer to input simplified design choices and enables TouchHub to automatically create optimized tuning configurations. Additionally, a digitizer driver is available for Linux.

# Features at a glance

### **Capacitive Multi-touch controller**

- Ultra high SNR: >80dB

- Supports up to 198 touch sensing channels and a maximum of 6144 sensing nodes<sup>1</sup>

- Flexible channel routing allows arbitrary touch sensor aspect ratios

- Supports large ultra-wide aspect ratio sensors (over 5:1)

- Concurrently supports 2D (xy), 1D (slider) and 0D (button) sensors

- Touch sensing through very thick plastic lenses and/or air gaps

- Supports non-uniform lens thickness

- All touches reported at a frame rate of up to 250Hz<sup>2</sup>

- Glove support without switching modes

- Water suppression and wet finger tracking

- Low emissions, low drive amplitude, high immunity to conducted interference

- Host connection using SPI or I2C slave with interrupt

- 3V3 and 1V8 supply, no high voltage generators needed

- Independent I/O voltage supporting 1.8V to 3.3V host signaling

- Optional external synchronization with display drivers for highest SNR

### **General**

- Register based tuning with non-volatile configuration storage

- Field upgradable firmware

- Sophisticated Built-In-Self-Test routines and diagnostics

- Automotive AEC-Q100 grade 2 qualified<sup>3</sup>

- $-40^{\circ}$ C to  $+105^{\circ}$ C ambient operating temperature

- Available in LQFP256 package

- TouchHub evaluation and support software for design and tuning

<sup>&</sup>lt;sup>1</sup>Example: largest square sensor is 78x78 channels

<sup>&</sup>lt;sup>2</sup>Subject to configuration

<sup>&</sup>lt;sup>3</sup>Pending

# 2 Ordering Information

| Device      | Package       | Order Code                    | Shipping       | FW       |

|-------------|---------------|-------------------------------|----------------|----------|

|             |               |                               |                | Revision |

| AX198A-2D   | LQFP256       | AX198A-2D -E-                 | 36 devices per | WX.YZ    |

| LQFP256     | Exposed Pad   | LQFP256-EP28281404-B-V1 Rwxyz | tray           |          |

| Engineering | 28x28x1.4x0.4 |                               |                |          |

| Samples     |               |                               |                |          |

| AX198A-2D   | LQFP256       | Contact TouchNetix for        | 36 devices per |          |

| LQFP256     | Exposed Pad   | availability                  | tray           |          |

| Industrial  | 28x28x1.4x0.4 |                               |                |          |

| AX198A-2D   | LQFP256       | Contact TouchNetix for        | 36 devices per |          |

| LQFP256     | Exposed Pad   | availability                  | tray           |          |

| Automotive  | 28x28x1.4x0.4 |                               |                |          |

# **Contents**

| Introduction                                                                                                                                                                                                                                                                       |                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 2 Ordering Information                                                                                                                                                                                                                                                             | 2                                                                |

| 3 Device Pinout  3.1 Pin Map  3.1.1 LQFP256  3.2 Pin Table  3.2.1 LQFP256  4 Pin Descriptions  4.1 A053, C047, D047, E047  4.2 SHIELD2DCTS  4.3 GND  4.4 VDDA  4.5 VDDC  4.6 VDDI  4.7 SLVnIRQ  4.8 SLVSDA / SCK  4.9 SLVSCL / nSS  4.10 SLVI2CADDRSEL / MOSI  4.11 nSLVI2C / MISO | 6<br>6<br>7<br>7<br>11<br>11<br>11<br>11<br>12<br>12<br>12<br>12 |

| 4.12 DNC                                                                                                                                                                                                                                                                           | 12<br>13                                                         |

| 6.1 Sensing Overview 6.2 Touch Sensing 6.2.1 2D (xy) Sensing 6.2.2 1D (slider) and 0D (button) Sensing 6.3 Variable Thickness Lenses 6.4 EMC Features 6.5 Water Suppression 6.6 Sensor Compatibility 6.7 Sensor Protection                                                         | 15<br>18<br>18<br>21<br>23<br>24<br>26<br>28                     |

| 7 Host Interfaces 7.1 Available Interfaces 7.2 Mode Selection 7.3 Slave I2C Mode 7.3.1 Slave Address Selection 7.3.2 Connections 7.3.3 I2C Protocol 7.4 Slave SPI Mode 7.4.1 Device Selection 7.4.2 Connections 7.4.3 SPI Protocol                                                 | 29<br>30<br>30<br>30<br>31<br>31                                 |

|                                                                                                                                                                                                                                                                                    | <br>•                                                            |

|                                                         | 33 |

|---------------------------------------------------------|----|

| 9.1 Absolute Maximum Ratings                            | 33 |

| 9.2 Operational Ratings                                 | 34 |

| 9.2.1 Operating Conditions                              | 34 |

| 9.2.2 Power Requirements                                |    |

| 9.2.3 Power Sequencing                                  | 34 |

| 9.2.4 Startup Time                                      | 34 |

| 9.2.5 Reduced Power Mode                                | 35 |

| 9.2.6 CMOS I/O Characteristics                          | 36 |

| 9.2.7 Slave I2C Characteristics                         | 37 |

| 9.2.8 Slave SPI Characteristics                         | 38 |

| 9.2.9 Master I2C Characteristics                        |    |

| 9.2.10 Capacitance Ranges and Drive Limits              |    |

| 9.2.11 Non-volatile Memory Characteristics              |    |

| 9.2.12 Device BIST Capabilities                         |    |

| 9.2.13 Sensor BIST Capabilities                         |    |

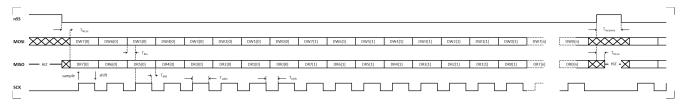

| 9.2.14 2D CTS Diagonal Size Range Guide                 |    |

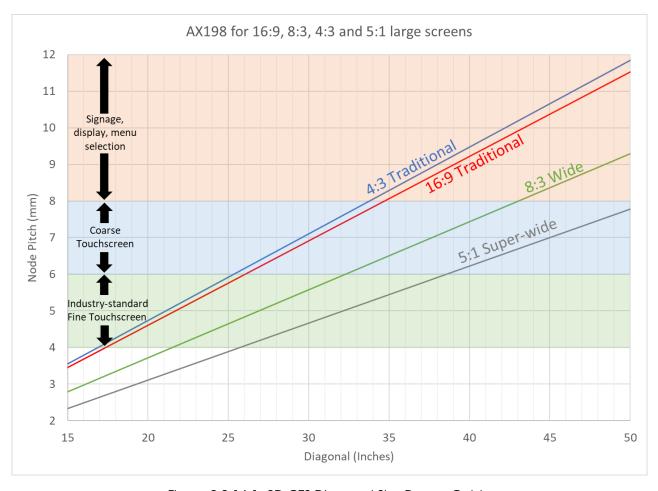

| Appendix A Package Drawings                             | 44 |

| A.1 LQFP256-EP28281404                                  | 44 |

| A.1.1 Layout and Routing Considerations for VDDA tracks | 45 |

| A.1.2 Package Thermal Characteristics                   |    |

| A.1.3 PCB Footprint Notes                               |    |

| Appendix B References                                   | 48 |

| Appendix C Legal Copyright and Disclaimer               | 49 |

| Appendix D Document History                             | 50 |

# **List of Figures**

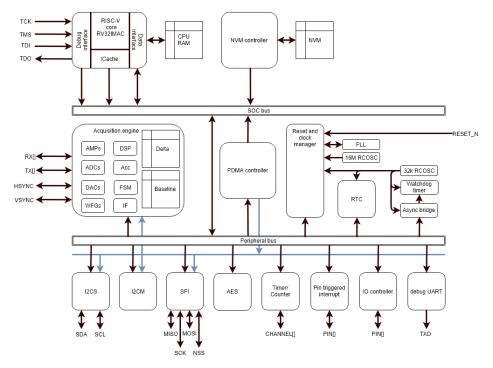

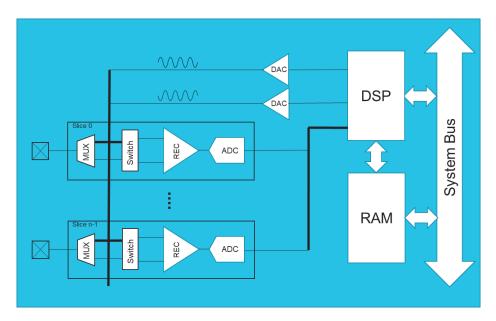

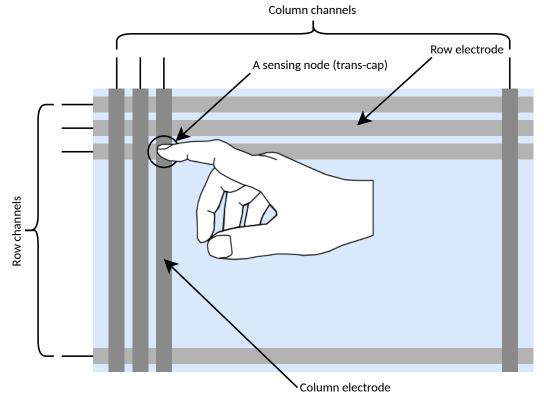

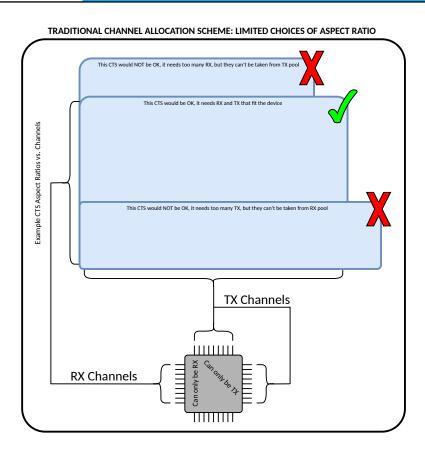

| I-I axiom 2D louch Sensing                                                                 |                |        |

|--------------------------------------------------------------------------------------------|----------------|--------|

| 3.1.1-1 LQFP256 Device Pinout (top view)                                                   |                | <br>6  |

| 5-1 Reference Schematic (LQFP256)                                                          |                | <br>14 |

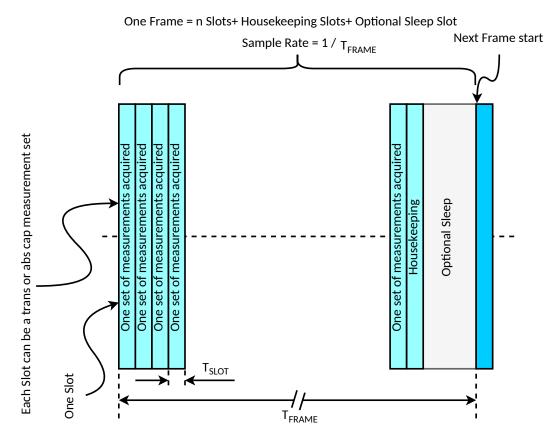

| 6.1-1 Acquisition Engine Frame Structure                                                   |                | <br>16 |

| 6.1-2 Simplified System Architecture                                                       |                |        |

| 6.1-3 Simplified Sensing Architecture                                                      |                |        |

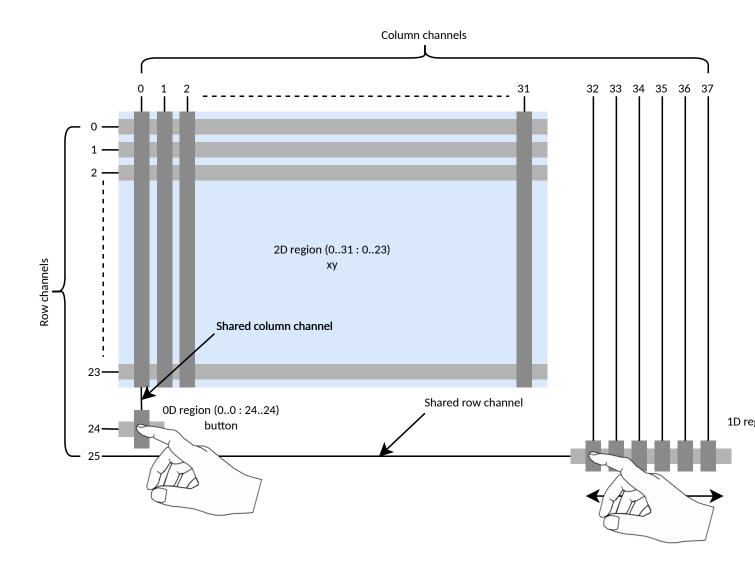

| 6.2.1-1 Channel Naming Convention                                                          |                |        |

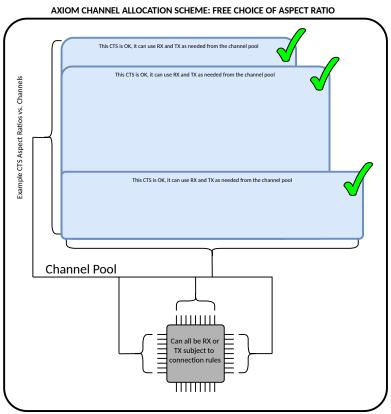

| 6.2.1-2 Traditional vs. aXiom Channel Allocation                                           |                |        |

| 6.2.2-1 Region Types                                                                       |                |        |

| 6.3-1 Example of a Flat Sensor and Variable Thickness Lens                                 |                | <br>23 |

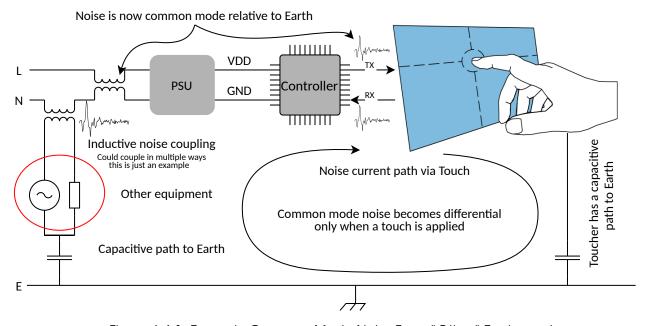

| 6.4-1 Example Common Mode Noise From "Other" Equipment                                     |                |        |

| 6.5-1 Different Behaviors With Abs-cap and Trans-cap Measurements With Water and Touc      | h.             | <br>26 |

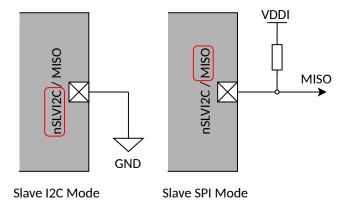

| 7.2-1 Communication Mode Selection                                                         | <i>-</i> 111 . | <br>20 |

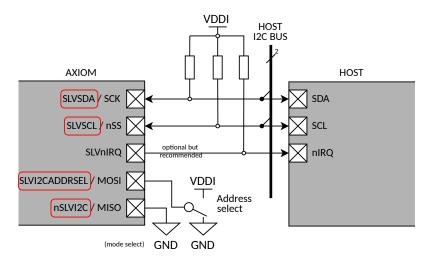

| 7.3.2-1 Slave I2C Connections                                                              |                |        |

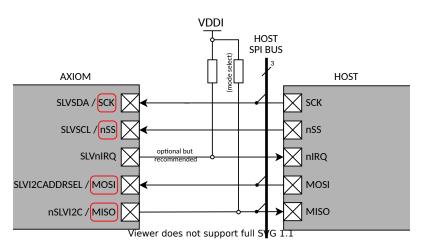

| 7.4.2-1 Slave SPI Connections                                                              |                |        |

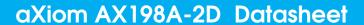

| 9.2.7-1 Typical I2C Transaction and Parameters                                             |                |        |

| 9.2.8-1 Typical SPI Transaction and Parameters                                             |                |        |

| 9.2.14-1 2D CTS Diagonal Size Range Guide                                                  |                |        |

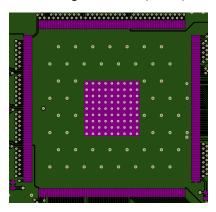

| A.1-1 LQFP256 Exposed Pad 28x28x1.4x0.4 Package Drawing                                    |                |        |

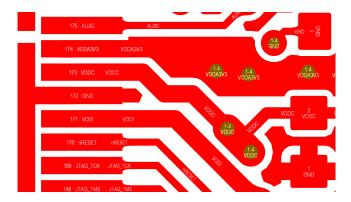

| A.1.1-1 C-shaped power routing, balanced amongst all VDDA pins                             |                |        |

| A.1.1-2 Note the use of the widest possible tracking and multiple vias for all VDD tracks. |                |        |

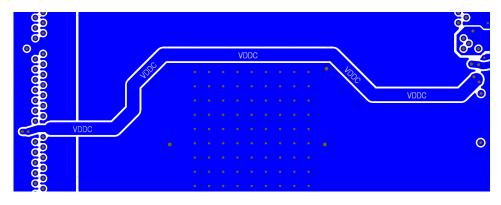

| A.1.1-3 Note the wide tracking joining all VDDC pins                                       |                |        |

| A.T.1-5 Note the wide flacking joining all VDDC pills.                                     |                | <br>40 |

|                                                                                            |                |        |

| List of Tables                                                                             |                |        |

|                                                                                            |                |        |

| 3.2.1-1 LQFP256 Pin Table                                                                  |                | <br>10 |

| 3.2.1-2 Pin Classes                                                                        |                |        |

| 7.3.1-1 Slave I2C Address Selection                                                        |                |        |

| 9.1-1 Absolute Maximum Ratings                                                             |                |        |

| 9.2.1-1 Operating Conditions                                                               |                | 34     |

| 9.2.2-1 Power Requirements                                                                 |                |        |

| 9.2.6-1 CMOS I/O Characteristics                                                           |                |        |

| 9.2.7-1 Timings                                                                            |                |        |

| 9.2.8-1 Timings                                                                            |                |        |

| 9.2.10-1 Capacitance Ranges and Drive Limits                                               |                |        |

| 9.2.11-1 Non-volatile Memory Characteristics                                               |                |        |

|                                                                                            |                |        |

# 3 Device Pinout

- 3.1 Pin Map

- 3.1.1 LQFP256

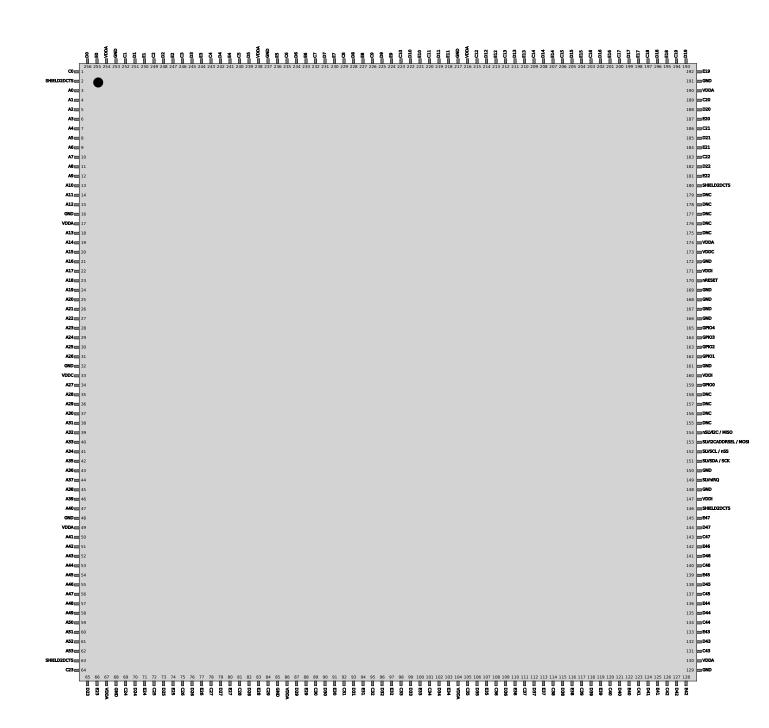

Figure 3.1.1-1: LQFP256 Device Pinout (top view)

Doc: TNxD00395 Pg: 6 of 50 Rev: A1

# 3.2 Pin Table

# 3.2.1 LQFP256

| Pin<br>Number | Name        | Class      | Domain       | Function                                    | If not required                                | Notes                                                      |

|---------------|-------------|------------|--------------|---------------------------------------------|------------------------------------------------|------------------------------------------------------------|

| 1             | C0          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 2             | SHIELD2DCTS | AO         | VDDA         | 2DCTS shield pin                            | Not applicable                                 | Shield driver for 2DCTS sense pins                         |

| 3<br>4        | A0<br>A1    | AIO<br>AIO | VDDA<br>VDDA | Sense pin<br>Sense pin                      | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                            |

| 5             | A2          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 6             | A3          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 7             | A4          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 8             | A5          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 9             | A6          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 10            | A7          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 11            | A8          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 12<br>13      | A9          | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                            |

| 14            | A10<br>A11  | AIO<br>AIO | VDDA<br>VDDA | Sense pin<br>Sense pin                      | Connect to SHIELD2DCTS                         |                                                            |

| 15            | A12         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 16            | GND         | PWR        |              | Supply and signal reference                 | Not applicable                                 |                                                            |

| 17            | VDDA        | PWR        |              | Analogue supply                             | Not applicable                                 |                                                            |

| 18            | A13         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 19            | A14         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 20            | A15         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 21<br>22      | A16         | AIO<br>AIO | VDDA<br>VDDA | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 22            | A17<br>A18  | AIO        | VDDA         | Sense pin<br>Sense pin                      | Connect to SHIELD2DCTS Connect to SHIELD2DCTS  |                                                            |

| 24            | A19         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 25            | A20         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 26            | A21         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 27            | A22         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 28            | A23         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 29            | A24         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 30            | A25         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 31<br>32      | A26<br>GND  | AIO<br>PWR | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS  Not applicable         |                                                            |

| 33            | VDDC        | PWR        |              | Supply and signal reference  Core supply    | Not applicable                                 | Output from internal LDO                                   |

| 34            | A27         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Guipar non milanares                                       |

| 35            | A28         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 36            | A29         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 37            | A30         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 38            | A31         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 39            | A32         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 40<br>41      | A33<br>A34  | AIO<br>AIO | VDDA<br>VDDA | Sense pin<br>Sense pin                      | Connect to SHIELD2DCTS Connect to SHIELD2DCTS  |                                                            |

| 42            | A35         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 43            | A36         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as C48                               |

| 44            | A37         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as D48                               |

| 45            | A38         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as E48                               |

| 46            | A39         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as C49                               |

| 47            | A40         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as D49                               |

| 48            | GND         | PWR        |              | Supply and signal reference                 | Not applicable                                 |                                                            |

| 49<br>50      | VDDA<br>A41 | PWR<br>AIO | VDDA         | Analogue supply Sense pin                   | Not applicable Connect to SHIELD2DCTS          | Can be aliased to act as E49                               |

| 51            | A42         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as C50                               |

| 52            | A43         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as C50                               |

| 53            | A44         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as E50                               |

| 54            | A45         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as C51                               |

| 55            | A46         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as D51                               |

| 56            | A47         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as E51                               |

| 57            | A48         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as C52 Can be aliased to act as D52  |

| 58<br>59      | A49<br>A50  | AIO<br>AIO | VDDA<br>VDDA | Sense pin<br>Sense pin                      | Connect to SHIELD2DCTS Connect to SHIELD2DCTS  | Can be aliased to act as D52 Can be aliased to act as E52  |

| 60            | A50<br>A51  | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS | Can be aliased to act as E52  Can be aliased to act as C53 |

| 61            | A52         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as C53                               |

| 62            | A53         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         | Can be aliased to act as E53                               |

| 63            | SHIELD2DCTS | AO         | VDDA         | 2DCTS shield pin                            | Not applicable                                 | Shield driver for 2DCTS sense pins                         |

| 64            | C23         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 65            | D23         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 66            | E23         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 67<br>68      | VDDA<br>GND | PWR<br>PWR |              | Analogue supply Supply and signal reference | Not applicable  Not applicable                 |                                                            |

| 69            | GND<br>C24  | AIO        | VDDA         | Supply and signal reference<br>Sense pin    | Connect to SHIELD2DCTS                         |                                                            |

| 70            | D24         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 71            | E24         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 72            | C25         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 73            | D25         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 74            | E25         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| 75            | C26         | AIO        | VDDA         | Sense pin                                   | Connect to SHIELD2DCTS                         |                                                            |

| Pin<br>Number | Name        | Class      | Domain       | Function                              | If not required                                | Notes                               |

|---------------|-------------|------------|--------------|---------------------------------------|------------------------------------------------|-------------------------------------|

| 76            | D26         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 77            | E26         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 78            | C27         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 79            | D27         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 80            | E27         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 81<br>82      | C28<br>D28  | AIO<br>AIO | VDDA<br>VDDA | Sense pin<br>Sense pin                | Connect to SHIELD2DCTS Connect to SHIELD2DCTS  |                                     |

| 83            | E28         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 84            | C29         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 85            | GND         | PWR        |              | Supply and signal reference           | Not applicable                                 |                                     |

| 86            | VDDA        | PWR        |              | Analogue supply                       | Not applicable                                 |                                     |

| 87            | D29         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 88            | E29         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 89            | C30         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 90            | D30         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 91            | E30         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 92            | C31         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 93            | D31         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 94            | E31         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 95            | C32         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 96<br>97      | D32<br>E32  | AIO<br>AIO | VDDA<br>VDDA | Sense pin                             | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                     |

| 98            | C33         | AIO        | VDDA         | Sense pin<br>Sense pin                | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                     |

| 99            | D33         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 100           | E33         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 101           | C34         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 102           | D34         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 103           | E34         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 104           | VDDA        | PWR        |              | Analogue supply                       | Not applicable                                 |                                     |

| 105           | C35         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 106           | D35         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 107           | E35         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 108           | C36         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 109           | D36         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 110           | E36         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 111           | C37         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 112           | D37         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 113<br>114    | E37<br>C38  | AIO<br>AIO | VDDA<br>VDDA | Sense pin                             | Connect to SHIELD2DCTS Connect to SHIELD2DCTS  |                                     |

| 115           | D38         | AIO        | VDDA         | Sense pin<br>Sense pin                | Connect to SHIELD2DCTS                         |                                     |

| 116           | E38         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 117           | C39         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 118           | D39         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 119           | E39         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 120           | C40         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 121           | D40         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 122           | E40         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 123           | C41         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 124           | D41         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 125           | E41         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 126           | C42         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 127           | D42         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 128<br>129    | E42<br>GND  | AIO<br>PWR | VDDA         | Sense pin Supply and signal reference | Connect to SHIELD2DCTS  Not applicable         |                                     |

| 130           | VDDA        | PWR        |              | Analogue supply                       | Not applicable                                 |                                     |

| 131           | C43         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 132           | D43         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 133           | E43         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 134           | C44         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 135           | D44         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 136           | E44         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 137           | C45         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 138           | D45         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 139           | E45         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 140           | C46         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 141           | D46         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 142           | E46         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 143           | C47         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 144           | D47         | AIO        | VDDA         | Sense pin                             | Connect to SHIELD2DCTS                         |                                     |

| 145           | E47         | AIO        | VDDA         | Sense pin<br>2DCTS shield pin         | Connect to SHIELD2DCTS                         | Chief driver for CDCTC sense mine   |

| 146<br>147    | SHIELD2DCTS | AO<br>PWR  | VDDA         | 2DC1S shield pin<br>I/O supply        | Not applicable                                 | Shield driver for 2DCTS sense pins  |

| 147           | VDDI<br>GND | PWR        |              | Supply and signal reference           | Not applicable Not applicable                  |                                     |

| 140           | SLVnIRQ     | OD         | VDDI         | Slave report ready interrupt          | Leave no connect                               | Requires additional pull up if used |

| 149           |             |            |              |                                       |                                                |                                     |

| Pin<br>Number | Name                 | Class                                                    | Domain       | Function                                                | If not required                                | Notes                                                                                                  |

|---------------|----------------------|----------------------------------------------------------|--------------|---------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 151           | SLVSDA / SCK         | ODwpu<br>(may<br>change<br>to lwpu<br>during<br>startup) | VDDI         | Slave I2C data OR SPI SCK                               | Not applicable                                 | Requires additional pull up if using I2C mode.                                                         |

| 152           | SLVSCL / nSS         | ODwpu<br>(may<br>change<br>to lwpu<br>during<br>startup) | VDDI         | Slave I2C clock OR SPI nSS                              | Not applicable                                 | Requires additional pull up if using I2C mode.                                                         |

| 153           | SLVI2CADDRSEL / MOSI | lwpu                                                     | VDDI         | Slave I2C address select OR<br>SPI MOSI                 | Not applicable                                 | In I2C mode, controls address. In SPI mode becomes<br>MOSI input from host                             |

| 154           | nSLVI2C / MISO       | (may<br>change<br>to O<br>during<br>startup)             | VDDI         | Slave I2C mode OR SPI MISO                              | Not applicable                                 | Sampled at reset; if low selects I2C mode, if high selects<br>SPI mode and becomes MISO output to host |

| 155           | DNC                  |                                                          |              | Do not connect                                          |                                                |                                                                                                        |

| 156<br>157    | DNC<br>DNC           |                                                          |              | Do not connect  Do not connect                          |                                                |                                                                                                        |

| 157           | DNC                  |                                                          |              | Do not connect                                          |                                                |                                                                                                        |

| 159           | GPIO0                | lOwpu                                                    | VDDI         | General purpose I/O                                     | Leave no connect                               |                                                                                                        |

| 160           | VDDI                 | PWR                                                      |              | I/O supply                                              | Not applicable                                 |                                                                                                        |

| 161           | GND                  | PWR                                                      |              | Supply and signal reference                             | Not applicable                                 |                                                                                                        |

| 162<br>163    | GPIO1<br>GPIO2       | IOwpu<br>IOwpu                                           | VDDI<br>VDDI | General purpose I/O General purpose I/O                 | Leave no connect Leave no connect              | Optionally serves as HSYNC input Optionally serves as VSYNC/EXTSYNC input                              |

| 164           | GPIO2<br>GPIO3       | lOwpu                                                    | VDDI         | General purpose I/O                                     | Leave no connect                               | Optionally serves as votivo/Existivo IIIpul                                                            |

| 165           | GPIO4                | IOwpu                                                    | VDDI         | General purpose I/O                                     | Leave no connect                               |                                                                                                        |

| 166           | GND                  | PWR                                                      |              | Supply and signal reference                             | Not applicable                                 |                                                                                                        |

| 167           | GND                  | PWR<br>PWR                                               |              | Supply and signal reference                             | Not applicable                                 |                                                                                                        |

| 168<br>169    | GND<br>GND           | PWR                                                      |              | Supply and signal reference Supply and signal reference | Not applicable  Not applicable                 |                                                                                                        |

| 170           | nRESET               | lwpu                                                     | VDDI         | Hardware reset                                          | Not applicable                                 | May require additional bypass capacitor to GND for best                                                |

|               |                      |                                                          | VDDI         |                                                         | ' '                                            | EMC                                                                                                    |

| 171<br>172    | VDDI<br>GND          | PWR<br>PWR                                               |              | I/O supply Supply and signal reference                  | Not applicable  Not applicable                 |                                                                                                        |

| 172           | VDDC                 | PWR                                                      |              | Core supply                                             | Not applicable                                 | Output from internal LDO                                                                               |

| 174           | VDDA                 | PWR                                                      |              | Analogue supply                                         | Not applicable                                 |                                                                                                        |

| 175           | DNC                  |                                                          |              | Do not connect                                          |                                                |                                                                                                        |

| 176<br>177    | DNC<br>DNC           |                                                          |              | Do not connect  Do not connect                          |                                                |                                                                                                        |

| 177           | DNC                  |                                                          |              | Do not connect                                          |                                                |                                                                                                        |

| 179           | DNC                  |                                                          |              | Do not connect                                          |                                                |                                                                                                        |

| 180           | SHIELD2DCTS          | AO                                                       | VDDA         | 2DCTS shield pin                                        | Not applicable                                 | Shield driver for 2DCTS sense pins                                                                     |

| 181<br>182    | E22<br>D22           | AIO<br>AIO                                               | VDDA<br>VDDA | Sense pin                                               | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 183           | C22                  | AIO                                                      | VDDA         | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS                         |                                                                                                        |

| 184           | E21                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 185           | D21                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 186<br>187    | C21<br>E20           | AIO                                                      | VDDA<br>VDDA | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 188           | D20                  | AIO<br>AIO                                               | VDDA         | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 189           | C20                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 190           | VDDA                 | PWR                                                      |              | Analogue supply                                         | Not applicable                                 |                                                                                                        |

| 191<br>192    | GND                  | PWR                                                      | \/DDA        | Supply and signal reference                             | Not applicable                                 |                                                                                                        |

| 192           | E19<br>D19           | AIO<br>AIO                                               | VDDA<br>VDDA | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 194           | C19                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 195           | E18                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 196<br>197    | D18<br>C18           | AIO<br>AIO                                               | VDDA<br>VDDA | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 197           | E17                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 199           | D17                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 200           | C17                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS Connect to SHIELD2DCTS  |                                                                                                        |

| 201<br>202    | E16<br>D16           | AIO<br>AIO                                               | VDDA<br>VDDA | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 203           | C16                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 204           | E15                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 205<br>206    | D15<br>C15           | AIO<br>AIO                                               | VDDA<br>VDDA | Sense pin                                               | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 206           | E14                  | AIO                                                      | VDDA         | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 208           | D14                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 209           | C14                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 210<br>211    | E13<br>D13           | AIO<br>AIO                                               | VDDA<br>VDDA | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 212           | C13                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 213           | E12                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 214           | D12                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 215<br>216    | C12<br>VDDA          | AIO<br>PWR                                               | VDDA         | Sense pin Analogue supply                               | Connect to SHIELD2DCTS  Not applicable         |                                                                                                        |

| 217           | GND                  | PWR                                                      |              | Supply and signal reference                             | Not applicable                                 |                                                                                                        |

| 218           | E11                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 219           | D11                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 220<br>221    | C11<br>E10           | AIO<br>AIO                                               | VDDA<br>VDDA | Sense pin<br>Sense pin                                  | Connect to SHIELD2DCTS  Connect to SHIELD2DCTS |                                                                                                        |

| 222           | D10                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 223           | C10                  | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 224           | E9                   | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         |                                                                                                        |

| 225           | D9                   | AIO                                                      | VDDA         | Sense pin                                               | Connect to SHIELD2DCTS                         | <u> </u>                                                                                               |

| Pin<br>Number | Name | Class | Domain | Function                    | If not required        | Notes |

|---------------|------|-------|--------|-----------------------------|------------------------|-------|

| 226           | C9   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 227           | E8   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 228           | D8   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 229           | C8   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 230           | E7   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 231           | D7   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 232           | C7   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 233           | E6   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 234           | D6   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 235           | C6   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 236           | E5   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 237           | GND  | PWR   |        | Supply and signal reference | Not applicable         |       |

| 238           | VDDA | PWR   |        | Analogue supply             | Not applicable         |       |

| 239           | D5   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 240           | C5   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 241           | E4   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 242           | D4   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 243           | C4   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 244           | E3   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 245           | D3   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 246           | C3   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 247           | E2   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 248           | D2   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 249           | C2   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 250           | E1   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 251           | D1   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 252           | C1   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 253           | GND  | PWR   |        | Supply and signal reference | Not applicable         |       |

| 254           | VDDA | PWR   |        | Analogue supply             | Not applicable         |       |

| 255           | EO   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

| 256           | D0   | AIO   | VDDA   | Sense pin                   | Connect to SHIELD2DCTS |       |

Table 3.2.1-1: LQFP256 Pin Table

| Class | Description                                      |

|-------|--------------------------------------------------|

| PWR   | Power pin                                        |

| Al    | Analogue input                                   |

| AO    | Analogue output                                  |

| AIO   | Analogue IO                                      |

| I     | CMOS input (no pull up)                          |

| lwpu  | CMOS input with weak pull up <sup>4</sup>        |

| 0     | CMOS push-pull output                            |

| ODwpu | CMOS Open drain with weak pull up <sup>4</sup>   |

| OD    | CMOS Open drain no pull up                       |

| Ю     | CMOS input/output                                |

| lOwpu | CMOS input/output with weak pull up <sup>4</sup> |

Table 3.2.1-2: Pin Classes

As a general convention, communication pin names are prefixed with "SLV" or "MST" to designate Slave or Master. Pin names with an "n" at the start of the function name designate an active-low signal e.g. MSTnIRQ is an active low interrupt from the Master. Also note that dual-mode pins are named (A) / (B), where (A) is the applicable name in the first mode and (B) in the second mode.

Doc: TNxD00395 Pg: 10 of 50 Rev: A1

<sup>&</sup>lt;sup>4</sup>Pull up/down intended as level keeper only.

# 4 Pin Descriptions

## 4.1 A0..53, C0..47, D0..47, E0..47

These are the sense pins, connected to the 2D CTS electrodes. The exact pin to electrode mapping is defined using the TouchHub configuration tool. The routing and layout of the connections to these pins is very important for best performance and is described in a separate application note. See **Appendix B References**. Note that A36 through A53 can be configured to act as C48 D48 E48 through to C53 D53 E53 in support of ultra-wide aspect ratio sensor designs.

#### 4.2 SHIELD2DCTS

The 2D CTS sense pins must be routed using a shielding technique using a dummy electrode that is driven by this pin. This is described in a separate application note. See **Appendix B References**. SHIELD2DCTS must be bypassed to GND near to the device, with a single 1nF 6V ceramic X5R (or tighter tolerance) capacitor.

### 4.3 **GND**

The OV power supply connection. Connect all GND pins to OV.

#### 4.4 VDDA

The analogue sub-system's power supply connection, running at nominally 3.3V. Connect all VDDA pins to 3.3V. The VDDA supply must be low noise and well regulated. Each VDDA pin must have a parallel 22uF and 100nF ceramic capacitor within 2mm, bypassing to GND with a short low inductance PCB trace. An additional single bulk ceramic, tantalum or electrolytic capacitor of  $\geq$  22uF is required on the VDDA supply. Under most conditions its is acceptable to share this supply with VDDI<sup>5</sup>.

These pins have special layout considerations. See **Appendix A.1.1 Layout and Routing Considerations** for VDDA tracks for further details.

# 4.5 VDDC

The core sub-system's power supply output, driven by an internal LDO running at nominally 1.8V. If there is more than one VDDC pin then connect them all together to form a single net. Each VDDC pin must have a parallel 22uF and 100nF ceramic capacitor within 2mm, bypassing to GND with a short low inductance PCB trace. No other connections to the VDDC net are permitted.

These pins have special layout considerations. See **Appendix A.1.1 Layout and Routing Considerations** for VDDA tracks for further details.

#### **4.6 VDDI**

The I/O sub-system's power supply connection, running at nominally 1.8V to 3.3V. Connect all VDDI pins to this supply. The VDDI supply is used to define the interface logic level used to communicate with the host. As such it must be sufficiently well regulated to ensure reliable high speed comms. Each VDDI pin must have a 100nF ceramic capacitor within 2mm, bypassing to GND with a short low inductance PCB trace. If the VDDA and VDDI supplies are separate then an additional single bulk ceramic, tantalum or electrolytic capacitor of  $\geq 1$ uF is required on the VDDI supply. Under most conditions it is OK to share this supply with VDDA in which case route VDDI as a separate net and use a star point connection to VDDA to help to isolate noise on the two domains<sup>5</sup>. CMOS I/O pins should never exceed the limitations stated in Table 9.1-1 (Vpc and Vpa) during power up, operation or power down.

These pins have special layout considerations. See **Appendix A.1.1 Layout and Routing Considerations** for VDDA tracks for further details.

Doc: TNxD00395 Pg: 11 of 50 Rev: A1

<sup>&</sup>lt;sup>5</sup>Assuming the I/O level is 3.3V

#### 4.7 SLVnIRQ

The device generates an interrupt whenever it has a report waiting to be read by the host. The slave interrupt pin asserts low in this case. It returns to a Hi-Z state when no reports are pending (but is weakly pulled up). The action of the host reading a report is to consume that report, and when all reports have been consumed the pin returns to Hi-Z (wpu). In order to affect an acceptably fast low-to-high transition in the presence of parasitic capacitance, an external pull up of 1K to 10K is required. The host device should use \*level\* triggering to sense the interrupt.

# 4.8 SLVSDA / SCK

This pin serves different functions depending on the communication mode selected by the nSLVI2C pin:

**Slave I2C Mode:** The pin serves as the I2C Data pin to connect to the host. It has a weak internal pull up which must be supplemented with a 1K to 10K pull up to achieve correct rise and fall times depending on capacitive loading.

**Slave SPI Mode:** This pin becomes the SPI SCK clock input from the host. In this mode no additional pull-up resistor is required.

# 4.9 SLVSCL / nSS

This pin serves different functions depending on the communication mode selected by the nSLVI2C pin:

**Slave I2C Mode:** This pin is the I2C Clock pin to connect to the host. It has a weak internal pull up which must be supplemented with a 1K to 10K pull up to achieve correct rise and fall times depending on capacitive loading.

**Slave SPI Mode:** This pin becomes the SPI active low Slave Select input from the host. In this mode no additional pull-up resistor is required.

# 4.10 SLVI2CADDRSEL / MOSI

This pin serves different functions depending on the communication mode selected by the nSLVI2C pin:

**Slave I2C Mode:** Selects between 2 addresses for the device. See **7.3.1 Slave Address Selection** for details. The pin includes a weak pull up. It is strongly recommended to terminate this pin directly to GND or VDDI (as required) to completely override this pull up (but only when in Slave I2C mode!). **Slave SPI Mode:** The pin becomes the MOSI input from the host.

# 4.11 nSLVI2C / MISO

This pin serves different functions depending on its state as sampled at power-on or reset:

**Sampled low at reset:** Selects Slave I2C communications mode. The pin includes a weak pull up. It is strongly recommended to terminate this pin directly to GND to select Slave I2C mode.

**Sampled high at reset**: Selects Slave SPI communications mode. The pin includes a weak pull up. It is strongly recommended to use a supplemental pull-up of 1K to 10K to select SPI mode; the pin must not be terminated directly to VDDI! On switching to SPI mode, the pin is changed to an output driver and is used as the MISO output to the host.

#### 4.12 DNC

Do not connect. This pin has an internal connection to the device and must not be connected externally.

### 4.13 GPIO0..4

General purpose I/O pins that can be configured and used by the host as required. Each one has an internal weak pull up included. Note the optional use of GPIO1 as an HSYNC input and GPIO2 as a VSYNC/EXTSYNC input (these optional selections are made via the device's configuration registers).

Doc: TNxD00395 Pg: 12 of 50 Rev: A1

#### 4.14 GND

Do not connect. This pin has an internal connection to the device and must not be connected externally.

# 4.15 nRESET

This pin is the asynchronus master hardware reset. Asserted low it returns the device to its reset state. When high, the device operates as normal. The pin has a weak internal pull up which must be supplemented with a 1K to 5K pull up and optionally a 20 to 50nF ceramic bypass capacitor to GND<sup>6</sup> (to offer the best fast-transient immunity in harsh EMI applications).

Doc: TNxD00395 Pg: 13 of 50 Rev: A1

<sup>&</sup>lt;sup>6</sup>Check the ability of the connected reset driver to support this capacitive load

# 5 Reference Schematic

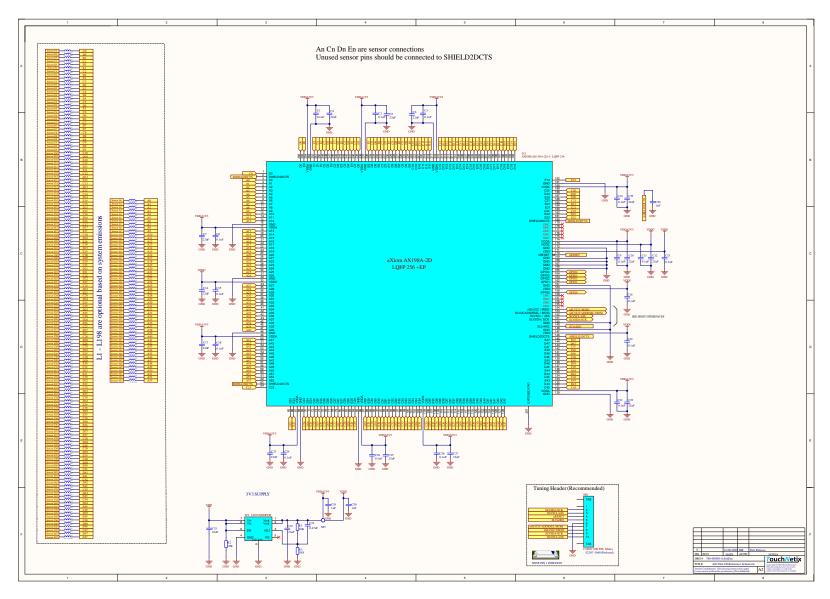

Figure 5-1: Reference Schematic (LQFP256)

aXiom AX198A-2D Datasheet

# 6 Sensing

# 6.1 Sensing Overview

The aXiom sensing architecture has been designed to measure capacitance, with a Signal-To-Noise ratio that goes far beyond existing solutions, whilst also being sympathetic to the diverse range of EMC and EMI challenges that are faced in real-world applications. Using a high purity narrow band drive waveform, with an amplitude of just 1.25V<sup>7</sup>, the controller not only has extremely low Radiated Emissions, but is also sympathetic to the long term sensor aging problem, that is seen when operating at elevated temperature and humidity. This little-documented aspect of touch sensors, can only be addressed by using low amplitude DC-neutral drive techniques, to radically slow-down the effects of electro-corrosion, electro-migration and e-field induced damage to various metals and some polymeric materials. To pass stringent EMC tests, in particular those dealing with injected currents (Conducted Immunity), many competing controllers resort to high sensor drive amplitudes to improve their overall SNR. While this may be successful in one regard, it seriously compromises both sensor lifetime and Radiated Emissions. Coupled with drive waveforms that are often square in nature (leading to complex harmonic content), it can be seen that a pure low amplitude drive signal is a major advantage in tough environments. To measure capacitance using small signals in the presence of large amounts external noise, requires that the sensing architecture and the analogue front end of the device, is carefully optimized to be able to recover the carrier, even when this is hundreds of times smaller than the interference; techniques that are well understood in modern radio systems but that are seldom used in touch sensing.

The device can be connected to a broad range of Capacitive Touch Sensor (CTS) styles, including both single and double connected versions of the well known *Diamond*, *Flooded* and *True Single Layer* types. To further extend the range of applications that are possible, the device treats its sensor pins as general resources and is able to use any pin as either drive or sense. This allows great flexibility in the aspect ratio of the CTS sensing area; the pool of sensor pins can be mapped to sensor electrodes in any ratio that is needed. This allows everything from long-thin touch areas to square touch areas to be created easily. The sensing architecture has more than enough dynamic range to handle the sensor measurement, in the presence of the diverse parasitics created by such extreme aspect ratios. This capability further extends to allowing direct support for truncated electrodes, often found in non-rectangular touch applications<sup>8</sup>.